# カスケード電圧スイッチ論理回路のSEU効果

### SEU Effects on Cascade Voltage Switch Logic Circuits

## 波多野 裕\* Hiroshi HATANO

Abstract: In order to design radiation-hardened LSIs for space applications, single-event-upset (SEU) effects on cascade voltage switch logic (CVSL) circuits have been investigated using SPICE. Static and dynamic CVSL circuits have been successfully fabricated utilizing a double polysilicon double metal  $1.2~\mu m$  CMOS technology. The both CVSL circuits have been confirmed to function correctly by the fabricated chip measurements. SEU simulation results have confirmed that the CVSL circuits have high SEU immunity. SEU immunity for the CVSL circuits is compared to that for the conventional CMOS circuits, showing that the CVSL is a candidate for a SEU immune spaceborne logic circuit.

#### 1. 緒言

宇宙環境で使用されるCMOS集積回路は放射線の電離作用の影響が積算されて半永久的特性劣化を生じさせるトータル・ドーズ効果や単一の高エネルギー荷電粒子によるラッチアップ現象や回路の一時的誤動作であるシングル・イベント・アップセット(SEU)に対する耐性強化が必要である<sup>1)</sup>。

われわれの研究室(電気電子工学科の光応用・電子デバイス分野)では、トランジスタ・レベルから回路設計を行い実際にチップを試作して、CMOS集積回路に対するSEU効果に関する一連の検討を行い、その結果の一部を既に報告してきた<sup>2)-5)</sup>。

本論文では、2系列の相補的なNMOSスイッチ構造と 1対の交差接続されたP形プルアップ・トランジスタから 構成するカスケード電圧スイッチ論理(CVSL)回路に 着目した。CVSL回路は真およびその相補値の両方の信 号を用いる2重系回路である。(なお、cascade から電子 回路用語 cascode<sup>12</sup>という造語が作られた。)

スタティック形及びダイナミック形CVSL回路を設計試作した。トランジスタ・レベルから回路設計を行い実際に  $1.2\mu$  mCMOSプロセス(実効チャネル長NMOS  $0.9\mu$  m、PMOS $0.8\mu$  m) $6^{0-10)}$  を用いてチップを試作して、試作チップの実測によりその機能動作を確認することに成功した。更に、この実測により機能動作を確認できた 2種類のCVSL回路に対するSEU耐性をシミュレーションにより検討したので、それぞれの結果を報告する。

#### 2. カスケード電圧スイッチ論理(CVSL)回路11)

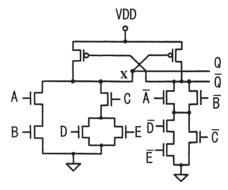

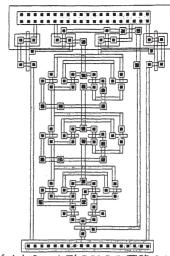

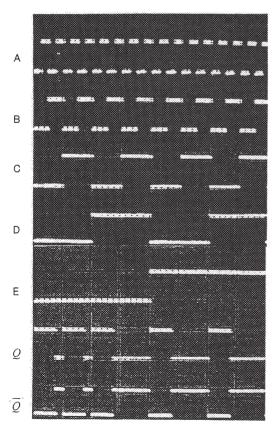

図 1 に今回設計したスタティック形CVSL回路のトランジスタ回路図を示す。論理演算A・B+C・(D+E)

$$Q = (A \cdot B) + [C \cdot (D + E)]$$

$$\overline{Q} = (\overline{A} + \overline{B}) \cdot [\overline{C} + (\overline{D} \cdot \overline{E})]$$

図1 スタティック形CVSL回路

$\frac{Q = A \oplus B \oplus C \oplus D}{Q = A \oplus B \oplus C \oplus D}$

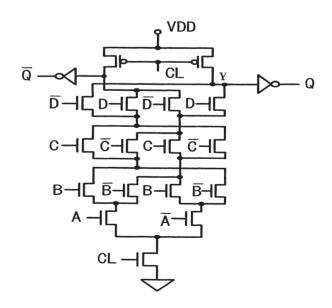

図2 ダイナミック形CVSL回路

20 Vol.16, 2 0 0 8

を実行する回路である。2つのPMOSと、真の信号を入力とする5つのNMOSおよび反転信号を入力とする5つのNMOSからなる2重系の構成である。

図 2 に今回設計したダイナミック形CVSL回路のトランジスタ回路図を示す。クロック形の4入力XOR回路であり、2系列のドミノ・ゲートと同じである。

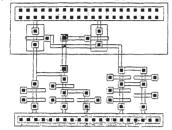

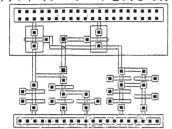

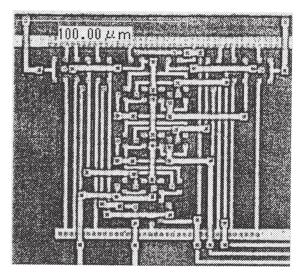

図3 スタティック形CVSL回路のレイアウト図

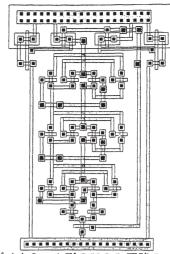

図4 ダイナミック形CVSL回路のレイアウト図

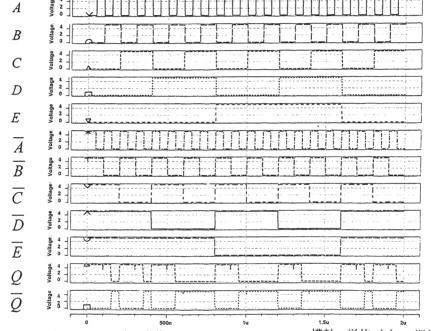

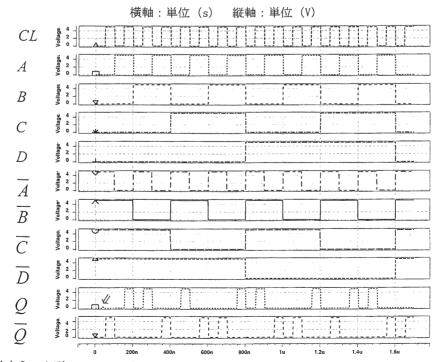

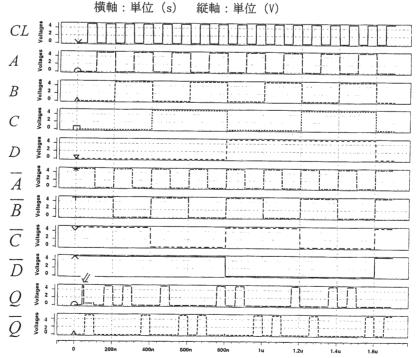

図5 スタティック形CVSL回路の動作シミュレーション 横軸:単位(s) 縦軸:単位(V)

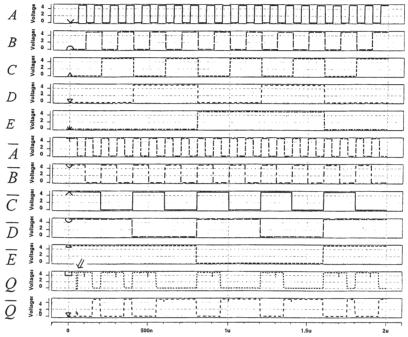

図6 ダイナミック形CVSL回路の動作シミュレーション 横軸:単位(s) 縦軸:単位(V)

を実行する回路である。2つのPMOSと、真の信号を入力とする 5つのNMOSおよび反転信号を入力とする 5つのNMOSからなる2重系の構成である。

図 2 に今回設計したダイナミック形CVSL回路のトランジスタ回路図を示す。クロック形の4入力XOR回路であり、2系列のドミノ・ゲートと同じである。

図4 ダイナミック形CVSL回路のレイアウト図

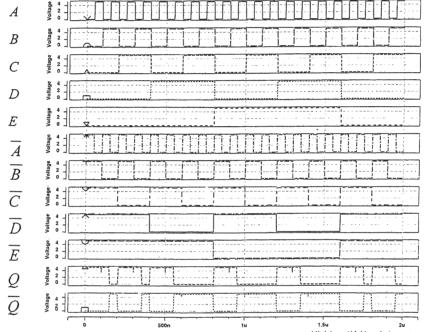

図5 スタティック形CVSL回路の動作シミュレーション 横軸:単位(s) 縦軸:単位(V)

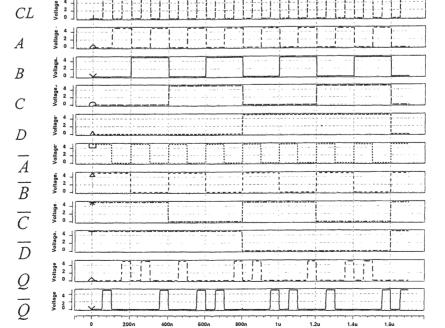

図 6 ダイナミック形CVSL回路の動作シミュレーション 横軸:単位(s) 縦軸:単位(V)

22 Vol.16, 2 0 0 8

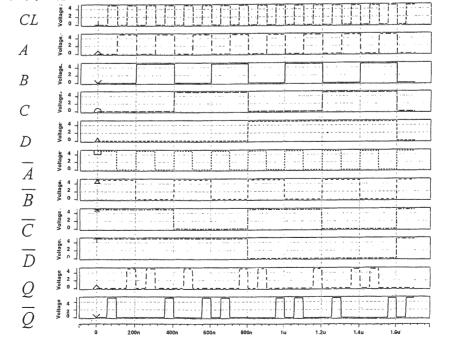

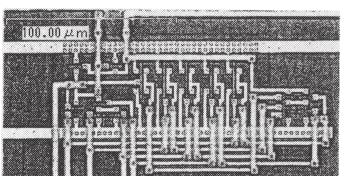

図 3 にスタティック形CVSL回路のレイアウト図を示す。 $1.2\,\mu$ m 2 層アルミNウエルCMOSデザインルールにより設計した。占有面積は $73\,\mu$ m× $56\,\mu$ m である。図 4 にダイナミック形CVSL回路のレイアウト図を示す。占有面積は $81\,\mu$ m× $120\,\mu$ m である。

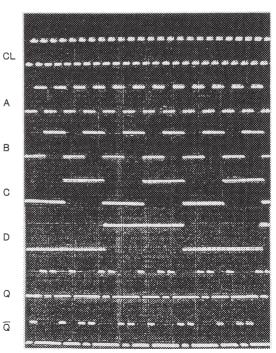

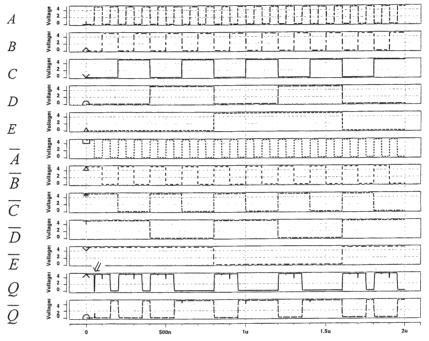

図 5 に、設計したスタティック形CVSL回路の機能動作を確認するために行った回路シミュレーションの結果を示す。Q出力およびその反転の出力の $\overline{Q}$ ともに期待値通りの結果が得られ正常動作が確認できた。図 6 に設計したダイナミック形CVSL回路の機能動作を確認するために行った回路シミュレーションの結果を示す。クロックCLがハイで回路が活性化されている場合、4入力のうち奇数個の入力が1のとき出力Qが 1 で、偶数個の入力が1のとき出力Qが 0、という正常なXOR(排他的論理和)動

図 7 スタティック形CVSL回路の顕微鏡写真

図 9 スタティック形CVSL回路の実測波形 横軸: 20 μ s/div. 縦軸: 5V/div.

作を確認することができた。反転の出力QはCLがハイのときQに対して反転していることも確認できた。

図 7 に  $1.2 \mu m$  2 層アルミNウエルCMOSプロセスで試作したスタティック形CVSL回路の顕微鏡写真を示す。NMOSトランジスタとPMOSトランジスタのゲート長は  $1.5 \mu$  mで、実効チャネル長がNMOSは  $0.9 \mu$  m、PMOSが  $0.8 \mu$  mである。ゲート酸化膜厚は 25 n mである。写真中央部分に反転入力発生回路を設けた。図 8 に試作したダイナミック形CVSL回路の顕微鏡写真を示す。回路部分の左右両側に反転入力発生回路を設けた。

図 9 に試作したスタティック形CVSL回路の実測波形を示す。図5のシミュレーション結果と比較して試作した回路が設計通り正常に動作していることを確認できた。図10に試作したダイナミック形CVSL回路の実測波形

図8 ダイナミック形CVSL回路の顕微鏡写真

図 10 ダイナミック形CVSL回路の実測波形 横軸:50 μ s/div. 縦軸:5V/div.

静岡理工科大学紀要 23

を示す。図6のシミュレーション結果と比較して試作した 回路が設計通り正常に動作していることを確認できた。

#### 3. SEUシミュレーション

CMOS回路内部の逆バイアス状態のPN接合に荷電粒子が照射されると空乏層に電荷が発生してPN接合をショートさせる。サブミクロンCMOSプロセスで試作されたLSIにおける荷電粒子の誘起電荷は約400 fCである $^{12.13}$ 。同一バイアス条件で、この電荷量を変化させ、回路動作への影響を観測して、回路のSEU耐性を検討した。

図1に示すスタティック形CVSL回路のノードXがハイ・レベルの状態でNMOSのPN接合が逆バイアスの時に荷電粒子が入射するという想定でシミュレーションを行った。

ノードXに回路シミュレータSPICEの独立電流源を接続した。1 ナノ秒の間、0.4 mAの電流を流すことにより、400 fC の電荷をノードXに発生させた。

50 ns の時刻において、ノードXに 400 fC の荷電粒子 誘起電荷が発生した場合のシミュレーション結果を図 11 に示す。出力Qの論理レベルの一時的低下が見られるが、

図 11 スタティック形CVSL回路のノードXに 400 fC の電荷が誘起された時のシミュレーション結果

図 12 ダイナミック形CVSL回路のノードYに 400 fC の電荷が誘起された時のシミュレーション結果 横軸:単位(s) 縦軸:単位(V)

Vol.16, 2 0 0 8

電荷が消えた後は元の1レベルに戻り、正しいデータ1を 示していることが分かる (矢印部分)。

次に、図2に示すダイナミック形CVSL回路のノード Yがハイ・レベルの状態でNMOSのPN接合が逆バイア スの時に荷電粒子が入射するという想定でシミュレーションを行った。

40 ns の時刻において、ノードYに 400 fC の荷電粒子 誘起電荷が発生した場合のシミュレーション結果を図 12 に示す。出力Qの論理レベル 0 が一時的に 0.6 V程度に 上昇するが、電荷が消えた後は元の 0 レベルに戻り、正し いデータ0を示していることが分かる(矢印部分)。

図 13 に、スタティック形CVSL回路のノードXに図 11 の 25 倍の 10 pC の荷電粒子誘起電荷が発生した場合の シミュレーション結果を示す。出力Qの論理レベルの一時 的低下が見られるが、電荷が消えた後は元の 1 レベルに戻り、正しいデータ 1 を示している (矢印部分)。更に 100 pC でも正常動作であった。

図 14 に、ダイナミック形CVSL回路のノードYに図 12 の 25 倍の 10 pC の荷電粒子誘起電荷が発生した場合の シミュレーション結果を示す。出力Qの論理 0 が一時的に

図 13 スタティック形CVSL回路のノードXに 10 pC の電荷が誘起された時のシミュレーション結果

図 14 ダイナミック形C V S L 回路のノードYに 10 pC の電荷が誘起された時のシミュレーション結果

横軸:単位(s) 縦軸:単位(V)

上昇したが、電荷が消えた後は元の0 レベルに戻り、正しいデータ0 を示した(矢印部分)。更に 100 pC の場合には出力Qの0 が1 と誤動作してS E U の発生を確認した。

以上のシミュレーション結果から、今回試作したCVS L回路は両者とも従来のCMOS回路の25倍以上のSE U耐性を持つことが判明した。

#### 4. 結言

宇宙用論理回路の候補の一つとして、スタティック形及びダイナミック形CVSL回路を設計試作した。トランジスタ・レベルから回路設計を行い実際に  $1.2\mu$ mCMOSプロセスを用いてチップを試作して、試作チップの実測によりスタティック形及びダイナミック形CVSL回路の機能動作を確認することに成功した。

更に、この実測により機能動作を確認できた2種類のCVSL回路に対するSEU耐性をシミュレーションにより検討した。その結果、試作したCVSL回路は通常のCMOS回路と比較して25倍以上のSEU耐性を備えていることが明らかになった。

### 謝辞

本研究に関するチップ試作は東京大学大規模集積システム設計教育研究センターを通しオンセミコンダクター (株)、日本モトローラ(株)、HOYA(株)、京セラ(株) の協力で行われたものである。

## 参考文献

- 1)波多野 裕, *耐環境CMOS超LSI*, (1996).

- 2)H. Hatano et al., "Radiation-hard CMOS VLSI logics for space applications", The Bulletin of Shizuoka Inst. of Sci. & Tech., vol.4, p.1-7, 1995.

- 3)波多野, 渋谷, 望月, "ナノ秒 6 トランジスタ CMOS スタティック RAM の設計試作(1)メモリ・セルと光ビーム照射実験",静岡理工科大学紀要, vol. 12, p. 109-118, 2004

- 4)波多野 裕,水口隆太郎, "宇宙用高信頼順序論理回路 の設計試作",静岡理工科大学紀要,vol.14,pp.31-35, 2006.

- 5) 波多野 裕, "宇宙用2重ラッチ回路のSEU効果", 静岡理工科大学紀要, vol.15, pp.73-76, 2007.

- T. Ochiai and H. Hatano," DC characteristic simulation for floating gate neuron MOS circuits", IEE Electronics Letters, vol.35. no. 18, pp.1505-1507, 1999.

- T. Ochiai and H. Hatano." A proposition on floating gate neuron MOS macromodeling for device fabrications", IEICE Trans. Fundamentals of Electronics, Communications and

Computer Sciences, vol.E82-A, no. 11, pp. 2485-2491, 1999.

- 8) T. Ochiai and H. Hatano," A low temperature DC analysis utilizing a floating gate neuron MOS macromodel", IEICE Trans. Electron., vol.E86-C, pp. 1114-1116, 2003.

- H. Hatano and T.Ochiai,"77K DC characteristics for floating gate neuron MOS circuits", Proceedings of 4 th European Workshop on Low Temperature Electronics,pp.271-275.

2000.

- 10) H. Hatano and T.Ochiai,"Neuron MOS circuit performance improvements by low temperature operation", Proceedings of 4 th European Workshop on Low Temperature Electronics, pp.49-53,2000.

- 11)成島晃久,"カスケード電圧スイッチ論理回路",静岡理工科大学2006年度卒業論文.

- 12) M. C. Casey et al.," HDB using cascode-voltage switch logic gates for SET tolerant digital designs", IEEE Trans. Nucl.Sci.,vol.52,no.6,pp.2510-2515,2005.

- 13) F. L. Kastensmidt, "SEE mitigation strategies for digital circuit design applicable to ASIC and FPGAs", 2007 IEEE Nuclear and Space Radiation Effects Conference.